# conga-QEVAL /Qseven® 2.0

Detailed description of the congatec Qseven® 2.0 evaluation carrier board

**User's Guide**

Revision 1.1

# **Revision History**

| Revision Date (yyyy.mm.dd) Author Changes |            |     | CI | nanges                                              |

|-------------------------------------------|------------|-----|----|-----------------------------------------------------|

| 1.0                                       | 2014.05.09 | AEM | •  | Official release                                    |

| 1.1                                       | 2015.01.15 |     | •  | Updated section 5.2.7 "Universal Serial Bus (USB)". |

|                                           |            |     | •  | Updated the User's Guide to revision B.2.           |

# **Preface**

This user's guide provides information about the components, features and connectors available on the conga-QEVAL/Qseven® 2.0 evaluation carrier board.

The conga-QEVAL/Qseven® 2.0 module is referred to as QEVAL 2.0 throughout this document.

### **Disclaimer**

The information contained within this user's guide, including but not limited to any product specification, is subject to change without notice.

congatec AG provides no warranty with regard to this user's guide or any other information contained herein and hereby expressly disclaims any implied warranties of merchantability or fitness for any particular purpose with regard to any of the foregoing. congatec AG assumes no liability for any damages incurred directly or indirectly from any technical or typographical errors or omissions contained herein or for discrepancies between the product and the user's guide. In no event shall congatec AG be liable for any incidental, consequential, special, or exemplary damages, whether based on tort, contract or otherwise, arising out of or in connection with this user's guide or any other information contained herein or the use thereof.

### **Intended Audience**

This user's guide is intended for technically qualified personnel. It is not intended for general audiences.

### **Lead-Free Designs (RoHS)**

All congatec AG products are created from lead-free components and are completely RoHS compliant.

### **Electrostatic Sensitive Device**

All electronic parts described in this user's guide are electrostatic sensitive devices and are packaged accordingly. Do not open or handle a carrier board or module except at an electrostatic-free workstation. Additionally, do not ship or store electronic devices near strong electrostatic, electromagnetic, magnetic, or radioactive fields unless the device is contained within its original manufacturer's packaging.

### **Symbols**

The following symbols are used in this user's guide:

### Warning

Warnings indicate conditions that, if not observed, can cause personal injury.

### Caution

Cautions warn the user about how to prevent damage to hardware or loss of data.

Notes call attention to important information that should be observed.

# Connector Type

Describes the connector that must be used with the Qseven® 2.0 evaluation carrier board, not the connector found on the Qseven® evaluation carrier board.

### Link to connector layout diagram

This link icon is located in the top left corner of each page. It provides a direct link to the connector layout diagram on page 10 of this document.

### **Copyright Notice**

Copyright © 2014, congatec AG. All rights reserved. All text, pictures and graphics are protected by copyrights. No copying is permitted without written permission from congatec AG.

congatec AG has made every attempt to ensure that the information in this document is accurate yet the information contained within is supplied "as-is".

### **Trademarks**

Product names, logos, brands, and other trademarks featured or referred to within this user's guide, or the congatec website, are the property of their respective trademark holders. These trademark holders are not affiliated with congatec AG, our products, or our website.

### **Warranty**

congatec AG makes no representation, warranty or guaranty, express or implied regarding the products except its standard form of limited warranty ("Limited Warranty") per the terms and conditions of the congatec entity, which the product is delivered from. These terms and conditions can be downloaded from www.congatec.com. congatec AG may in its sole discretion modify its Limited Warranty at any time and from time to time.

The products may include software. Use of the software is subject to the terms and conditions set out in the respective owner's license agreements, which are available at www.congatec.com and/or upon request.

Beginning on the date of shipment to its direct customer and continuing for the published warranty period, congated AG represents that the products are new and warrants that each product failing to function properly under normal use, due to a defect in materials or workmanship or due to non conformance to the agreed upon specifications, will be repaired or exchanged, at congated's option and expense.

Customer will obtain a Return Material Authorization ("RMA") number from congatec AG prior to returning the non conforming product freight prepaid. congatec AG will pay for transporting the repaired or exchanged product to the customer.

Repaired, replaced or exchanged product will be warranted for the repair warranty period in effect as of the date the repaired, exchanged or replaced product is shipped by congatec, or the remainder of the original warranty, whichever is longer. This Limited Warranty extends to congatec's direct customer only and is not assignable or transferable.

Except as set forth in writing in the Limited Warranty, congatec makes no performance representations, warranties, or guarantees, either express or implied, oral or written, with respect to the products, including without limitation any implied warranty (a) of merchantability, (b) of fitness for a particular purpose, or (c) arising from course of performance, course of dealing, or usage of trade.

congatec AG shall in no event be liable to the end user for collateral or consequential damages of any kind. congatec shall not otherwise be liable for loss, damage or expense directly or indirectly arising from the use of the product or from any other cause. The sole and exclusive remedy against congatec, whether a claim sound in contract, warranty, tort or any other legal theory, shall be repair or replacement of the product only.

### Certification

congatec AG is certified to DIN EN ISO 9001 standard.

### **Technical Support**

congatec AG technicians and engineers are committed to providing the best possible technical support for our customers so that our products can be easily used and implemented. We request that you first visit our website at www.congatec.com for the latest documentation, utilities and drivers, which have been made available to assist you. If you still require assistance after visiting our website then contact our technical support department by email at support@congatec.com

### **Terminology**

| Term                  | Description                                                                                                                                                                            |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Express (PCIe)    | Peripheral Component Interface Express – next-generation high speed Serialized I/O bus                                                                                                 |

| PCI Express Lane      | One PCI Express Lane is a set of 4 signals that contains two differential lines for                                                                                                    |

|                       | Transmitter and two differential lines for Receiver. Clocking information is embedded into the data stream.                                                                            |

| x1, x2, x4, x16       | x1 refers to one PCI Express Lane of basic bandwidth; x2 to a collection of two PCI Express Lanes; etc Also referred to as x1, x2, x4 or x16 link.                                     |

| PCI Express Mini Card | PCI Express Mini Card add-in card is a small size unique form factor optimized for mobile computing platforms.                                                                         |

| MMCplus               | MMCplus was defined for first time in MMC System Specification v4.0. MMCplus is backward compatible with MMC. MMCplus has 13 pins.                                                     |

| SDIO card             | SDIO (Secure Digital Input Output) is a non-volatile memory card format developed for use in portable devices.                                                                         |

| USB                   | Universal Serial Bus                                                                                                                                                                   |

| SATA                  | Serial AT Attachment: serial-interface standard for hard disks                                                                                                                         |

| HDA                   | High Definition Audio                                                                                                                                                                  |

| S/PDIF                | S/PDIF (Sony/Philips Digital Interconnect Format) specifies a Data Link Layer protocol and choice of Physical Layer specifications for carrying digital                                |

|                       | audio signals between devices and stereo components.                                                                                                                                   |

| HDMI                  | High Definition Multimedia Interface. HDMI supports standard, enhanced, or high-definition video, plus multi-channel digital audio on a single cable.                                  |

| TMDS                  | Transition Minimized Differential Signaling. TMDS is a signaling interface defined by Silicon Image that is used for DVI and HDMI.                                                     |

| DVI                   | Digital Visual Interface is a video interface standard developed by the Digital Display Working Group (DDWG).                                                                          |

| LPC                   | Low Pin-Count: a low speed interface used for peripheral circuits such as Super I/O controllers, which typically combine legacy device support into a single IC.                       |

| I <sup>2</sup> C Bus  | Inter-Integrated Circuit Bus: is a simple two-wire bus with a software-defined protocol that was developed to provide the communications link between integrated circuits in a system. |

| SM Bus                | System Management Bus: is a popular derivative of the I <sup>2</sup> C-bus.                                                                                                            |

| CAN                   | Controller Area Network                                                                                                                                                                |

| SPI                   | Serial Peripheral Interface                                                                                                                                                            |

| GBE                   | Gigabit Ethernet                                                                                                                                                                       |

| LVDS                  | Low-Voltage Differential Signaling                                                                                                                                                     |

| DDC                   | Display Data Channel is an I <sup>2</sup> C bus interface between a display and a graphics adapter.                                                                                    |

| N.C.                  | Not connected                                                                                                                                                                          |

| N.A.                  | Not available                                                                                                                                                                          |

| T.B.D.                | To be determined                                                                                                                                                                       |

# **Contents**

| 1        | Introduction                                     | 8    | 5.2.13   | PCI Express Mini Card                 |    |

|----------|--------------------------------------------------|------|----------|---------------------------------------|----|

| 1.1      | Qseven® 2.0 Concept                              | 8    | 5.2.14   | Digital Display Interface (DDI)       | 39 |

| 1.2      | QEVAL 2.0                                        |      | 5.2.15   | SDIO Interface                        |    |

|          |                                                  |      | 5.2.15.1 | SD/MMC Card Socket                    |    |

| 2        | Jumper and DIP Switch Settings                   | 9    | 5.2.16   | CAN Bus                               | 40 |

| 3        | Connector Layout                                 | . 10 | 6        | Additional Features                   |    |

| 4        | Specifications                                   | 12   | 6.1      | Power Button                          |    |

| 7        | •                                                |      | 6.2      | Sleep Button                          |    |

| 4.1      | Mechanical Dimensions                            |      | 6.3      | Reset Button                          |    |

| 4.2      | Power Supply                                     |      | 6.4      | LID Button                            |    |

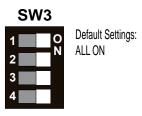

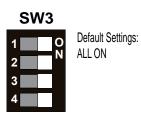

| 4.2.1    | PWR_OK Signal                                    | . 14 | 6.5      | Switch SW3                            | _  |

| 4.2.2    | Power Status LEDs D20-D25                        | . 14 | 6.6      | PC Speaker                            |    |

| 4.2.3    | Power-up Control                                 | . 14 | 6.7      | Debug Display                         |    |

| 4.3      | CMOS Battery                                     | . 15 | 6.8      | Onboard Module's COM Port             |    |

| 4.4      | Environmental Specifications                     |      | 6.9      | Internal Use Only Connectors          |    |

| 5        | Connector Description                            | 17   | 6.10     | Ground Probes                         |    |

|          | •                                                |      | 6.11     | External System Wake Event            |    |

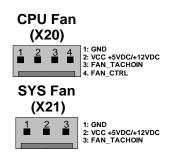

| 5.2.1    | SMBus                                            |      | 6.12     | Fan Connector and Power Configuration |    |

| 5.2.2    | I <sup>2</sup> C Bus                             |      | 6.13     | Feature Connector                     | 47 |

| 5.2.3    | SPI Bus                                          |      | 7        | QEVAL 2.0 Mechanical Drawing          | 48 |

| 5.2.4    | HDA Audio                                        |      | •        | QLV/L 2.0 Woorlandar Brawnig          |    |

| 5.2.5    | LPC Super I/O Device                             |      | 8        | Industry Specifications               | 49 |

| 5.2.5.1  | COM Ports                                        | . 25 |          |                                       |    |

| 5.2.5.2  | KBC Interface                                    | . 26 |          |                                       |    |

| 5.2.6    | LPC/GPIO Header                                  | . 26 |          |                                       |    |

| 5.2.7    | Universal Serial Bus (USB)                       | . 27 |          |                                       |    |

| 5.2.8    | Ethernet 10/100/1000                             | . 30 |          |                                       |    |

| 5.2.9    | Serial ATA™                                      | . 31 |          |                                       |    |

| 5.2.10   | Serial ATA™ Auxiliary Power                      | . 31 |          |                                       |    |

| 5.2.11   | LVDS Flat Panel Interface                        |      |          |                                       |    |

| 5.2.11.1 | Flat Panel and Backlight Power Supply            |      |          |                                       |    |

| 5.2.11.2 | Flat Panel and Backlight Power Supply Connection |      |          |                                       |    |

| 5.2.11.3 | Flat Panel Configuration Data                    |      |          |                                       |    |

| 5.2.12   | PCI Express Routing                              |      |          |                                       |    |

| _        | ,                                                |      |          |                                       |    |

# 1 Introduction

### 1.1 Qseven® 2.0 Concept

The Qseven® concept is an off-the-shelf, multi vendor, Computer-on-Module that integrates all the core components of a common PC and is mounted onto an application specific carrier board. Qseven® modules have standardized form factors of 70mm x 70mm and 70mm x 40mm, and specified pinout based on the high speed MXM system connector. The pinout is the same for all vendors. The Qseven® module provides the functional requirements for an embedded application. These functions include, but are not limited to, graphics, sound, mass storage, network interface and multiple USB ports.

A single ruggedized MXM connector provides the carrier board interface to carry all the I/O signals to and from the Qseven® module. This MXM connector is a well known and proven high speed signal interface connector that is commonly used for high speed PCI Express graphics cards in notebooks.

Carrier board designers can utilize as little or as many of the I/O interfaces as deemed necessary. The carrier board can therefore provide all the interface connectors required to attach the system to the application specific peripherals. This versatility allows the designer to create a dense and optimized package, which results in a more reliable product while simplifying system integration.

The Qseven® evaluation carrier board provides carrier board designers with a reference design platform and the opportunity to test all the Qseven® I/O interfaces available and then choose what are suitable for their application. Qseven® applications are scalable, which means once a carrier board has been created there is the ability to diversify the product range through the use of different performance class Qseven® modules. Simply unplug one module and replace it with another, no need to redesign the carrier board.

This document describes the features available on the Qseven® evaluation carrier board. Additionally, the schematics for the Qseven® evaluation carrier board can be found on the congatec website.

### 1.2 **QEVAL 2.0**

QEVAL 2.0 evaluation carrier board is designed according to Qseven® specification 2.0 and supports both x86 and ARM modules. With this dual architecture support, customers can test modules with different architectures on a single carrier board, thereby reducing production cost and time.

The customers however need to make sure the switches and jumpers for the shared pins are set correctly to avoid possible malfunction or damage to the module/carrier board.

# 2 Jumper and DIP Switch Settings

### Default Jumper and DIP Switch Settings for QEVAL 2.0

| 1      | Defeedt |

|--------|---------|

| Jumper | Default |

| X9     | 2-3     |

| X17    | 1-2     |

| X22    | 1-2     |

| X28    | 1-2     |

| X29    | 1-2     |

| X32    | 1-2     |

| X33    | 1-2     |

| X37    | 1-2     |

| X43    | 1-2     |

| Jumper | Default |

|--------|---------|

| X44    | 1-2     |

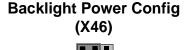

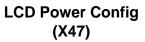

| X46    | 1-2     |

| X47    | 2-3     |

| X48    | 1-2     |

| X49    | 1-2     |

| X50    | 1-2     |

| X51    | 1-2     |

| X52    | 1-2     |

|        |         |

| DIP Switch | Switch 1 | Switch 2 | Switch 3 | Switch 4 |

|------------|----------|----------|----------|----------|

| SW1        | ON       | ON       | ON       | ON       |

| SW2        | ON       | ON       | OFF      | ON       |

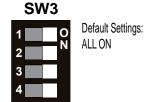

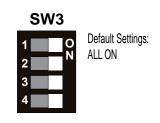

| SW3        | ON       | ON       | ON       | ON       |

| SW4        | ON       | ON       | ON       | ON       |

| SW9        | OFF      | OFF      | OFF      | OFF      |

| M13        | OFF      | OFF      |          |          |

### Required DIP Switch Settings when using conga-QMX6

| <b>DIP Switch</b> | Switch 1                  | Switch 2 | Switch 3 | Switch 4 | Comment                                                                                                                                                           |

|-------------------|---------------------------|----------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW1               | OFF                       | OFF      | OFF      | OFF      |                                                                                                                                                                   |

| SW2               | OFF                       | OFF      | OFF      | OFF      | conga-QMX6 does not support LPC Bus.                                                                                                                              |

| SW3               | ON                        | OFF      | OFF      | OFF      | FAN_PWMOUT / SPKR / FAN_TACHOIN signals are routed to a GPIO of the i.MX6 SoC (the signals must be implemented in the Kernel first before they can be functional) |

| SW4               | ON                        | ON       | ON       | ON       |                                                                                                                                                                   |

| SW9               | OFF                       | OFF      | OFF      | OFF      |                                                                                                                                                                   |

| M13               | OFF (BOOT_ALT#<br>Jumper) | OFF      |          |          | Dip 1 of Switch M13 must be set to 'ON' when updating the conga-QMX6 bootloader.                                                                                  |

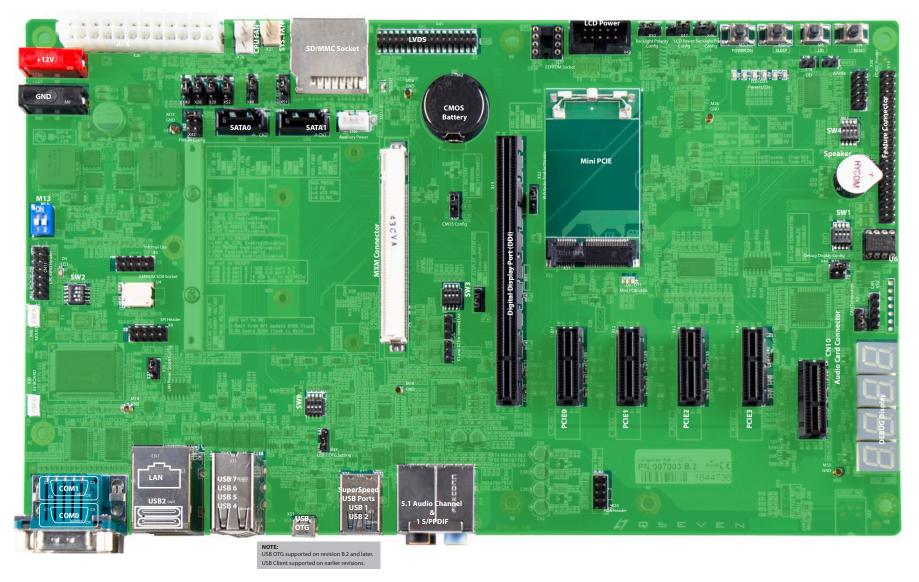

# 3 Connector Layout

The connector layout picture below shows each connector and its name designator. The Jumpers are also shown. Select the Adobe 'Zoom-In-Tool' and zoom in on a given component to see its designator. Hover over the component and the 'Zoom-In-Tool' will change indicating there is a link. Click on the link to navigate to the area in the document where the component is described. Use the mouse icon in the top left hand corner of the destination page to return to the connector layout picture.

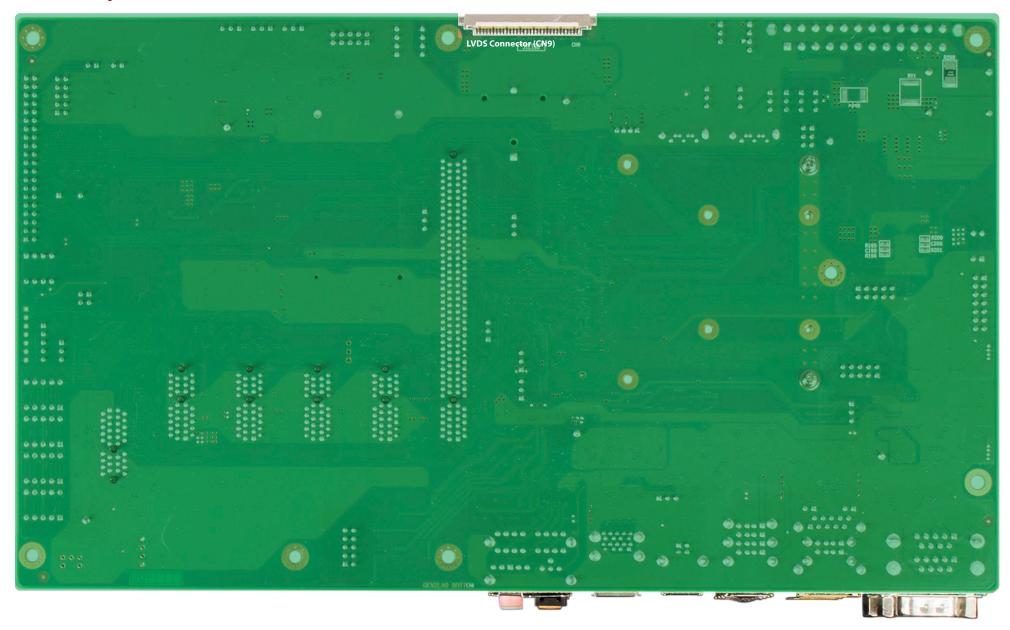

# **Connector Layout Bottom Side**

# 4 Specifications

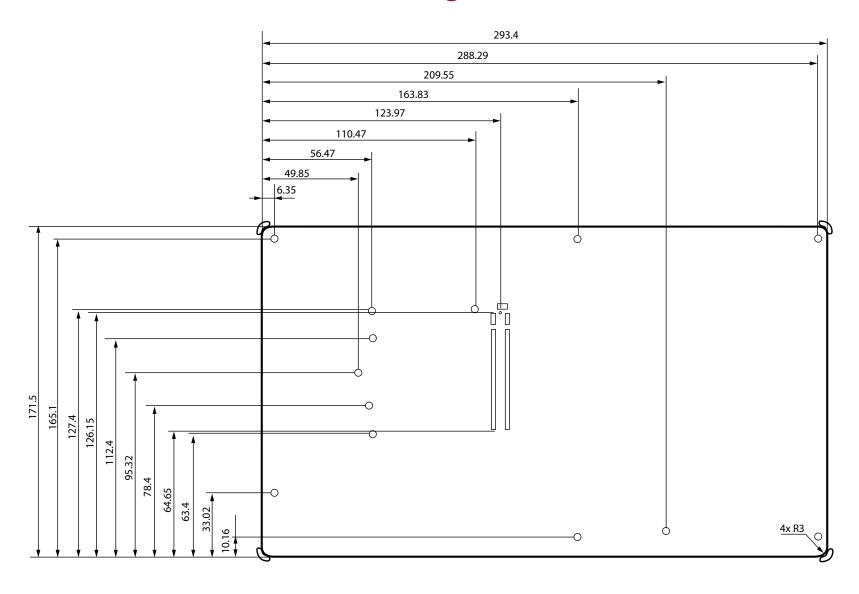

### 4.1 Mechanical Dimensions

- 293.4mm x 171.5mm

- Height approximately 37mm

# 4.2 Power Supply

The QEVAL 2.0 can be used with standard ATX (Connector X26) power supplies. The 3.3V, 5V and -12V power outputs of the ATX power supply are not used.

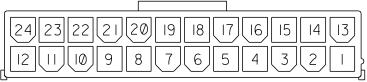

### **ATX Power Connector (X26)**

### **Connector X26 Pinout Description**

| Pin | Signal | Description                                                                                                                                                                 | Pin | Signal | Description                                                                                                       |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-------------------------------------------------------------------------------------------------------------------|

| 1   | +3.3V  | Power Supply +3.3VDC                                                                                                                                                        | 13  | +3.3V  | Power Supply +3.3VDC                                                                                              |

| 2   | +3.3V  | Power Supply +3.3VDC                                                                                                                                                        | 14  | -12V   | Power Supply -12VDC                                                                                               |

| 3   | GND    | Power Ground                                                                                                                                                                | 15  | GND    | Power Ground                                                                                                      |

| 4   | +5V    | Power Supply +5VDC                                                                                                                                                          | 16  | PS_ON# | Power Supply On (active low). Short this pin to GND to switch power supply ON, disconnect from GND to switch OFF. |

| 5   | GND    | Power Ground                                                                                                                                                                | 17  | GND    | Power Ground                                                                                                      |

| 6   | +5V    | Power Supply +5VDC                                                                                                                                                          | 18  | GND    | Power Ground                                                                                                      |

| 7   | GND    | Power Ground                                                                                                                                                                | 19  | GND    | Power Ground                                                                                                      |

| 8   | PWR_OK | Power Ok: A status signal generated by the power supply to notify the computer that the DC operating voltages are within the ranges required for proper computer operation. | 20  | NC     | Not connected                                                                                                     |

| 9   | 5V_SB  | Standby Power Supply +5VDC                                                                                                                                                  | 21  | +5V    | Power Supply +5VDC                                                                                                |

| 10  | +12V   | Power Supply +12DC                                                                                                                                                          | 22  | +5V    | Power Supply +5VDC                                                                                                |

| 11  | +12V   | Power Supply +12DC                                                                                                                                                          | 23  | +5V    | Power Supply +5VDC                                                                                                |

| 12  | +3.3V  | Power Supply +3.3VDC                                                                                                                                                        | 24  | GND    | Power Ground                                                                                                      |

When using an ATX power supply, the Qseven® module starts after you press the power-on button M3. The ATX power supply can also be used in AT mode. In this case the module starts when you turn on the power supply. Configure the power supply to ATX or AT mode with Jumper X29.

| Jumper X29 | Configuration                    |

|------------|----------------------------------|

| 1 - 2      | ATX Power supply (default)       |

| 2 - 3      | ATX Power supply runs in AT mode |

Connector Type

X29: 2.54mm grid Jumper.

You can isolate the carrier board's 5V standby power supply from the ATX 5V standby power supply with the Jumper X49. The isolation is ideal for test purposes.

| Jumper X49 | Configuration                         |

|------------|---------------------------------------|

| 1 - 2      | +5V_SB from ATX PSU enabled (default) |

| 2 - 3      | +5V SB from ATX PSU disabled          |

### Connector Type

X49: 2.54mm grid Jumper.

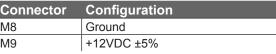

The QEVAL 2.0 can also be used with +12VDC power supply (connector M8 and M9). The +3.3V and +5V used by some devices on the QEVAL 2.0 are generated onboard from the +12V power supply.

| Connector | Configuration |

|-----------|---------------|

| M8        | Ground        |

| M9        | +12VDC ±5%    |

Connector Type

M8,M9: 4mm diameter plug

### 4.2.1 PWR\_OK Signal

The PWR\_OK (PWGIN) signal is a HIGH active input from the main power supply to the module and indicates whether the power is good. The Jumper X43 on the QEVAL 2.0 provides the ability to choose different settings for this signal.

| Jumper X43 | Configuration                                  |

|------------|------------------------------------------------|

| 1 - 2      | PWGIN generated by Pull-up resistor. (default) |

| 3 - 4      | PWGIN generated by ATX power source.           |

| 5 - 6      | PWGIN generated by DC/DC converter.            |

X43: 2.54mm grid Jumper.

### 4.2.2 Power Status LEDs D20-D25

The six green status LEDs D20-D25 indicate different power states of the QEVAL 2.0. See table below for more information.

| LEDs D20-D25 | Power state       |

|--------------|-------------------|

| All Off      | No power applied. |

| D20          | +5V standby       |

| D21          | +5V               |

| D22          | +3.3V standby     |

| D23          | +3.3V             |

| D24          | +5V standby input |

| D25          | +12V input        |

### 4.2.3 Power-up Control

The native system Power-up support of Qseven® modules uses the 'SUS\_S3#' signal to control the 'PS\_ON#' signal, which is used to switch the ATX power supply on or off. When using the SUS\_S3#' signal, the Qseven® module is capable of supporting Suspend to RAM (S3).

When the system goes to Suspend to RAM (S3) or Soft Off (S5), the 'SUS\_S3#' signal is asserted by the chipset of the module. Through the use of an inverter, the low active 'PS\_ON#' signal goes high and switches off the ATX power supply. On the contrary, if the system resides in a power-down system state, any system wake-up event invokes the chipset of the module to deassert the 'SUS\_S3#' signal. This transitions the system to Full-On (S0).

The way Suspend to RAM is implemented on a Qseven® module may differ depending on the module manufacturer. For this reason, it is

recommended to implement a hardware Jumper on the carrier board, to provide the ability to choose if the 'PS\_ON#' signal should be controlled by the 'SUS\_S3#' signal or the 'SUS\_S5#' signal. On the QEVAL 2.0, this is accomplished through the use of Jumper X28.

| Jumper X28 | Configuration                                 |

|------------|-----------------------------------------------|

| 1 - 2      | ATX Power supply controlled via S3# (default) |

| 2 - 3      | ATX Power supply controlled via S5#           |

X28: 2.54mm grid Jumper.

**CMOS Battery** (M2)

> **CMOS Battery** Config (X17)

### 4.3 **CMOS Battery**

The CMOS battery on connector M2 supplies power to the RTC and CMOS memory of the Qseven® module. The battery needs to provide 3V of power. The specified battery type is CR2032. It is possible to disconnect the CMOS battery using Jumper X17.

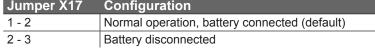

| Jumper X17 | Configuration                                 |

|------------|-----------------------------------------------|

| 1 - 2      | Normal operation, battery connected (default) |

| 2 - 3      | Battery disconnected                          |

# Connector Type

X17: 2.54mm grid Jumper.

Danger of explosion if battery is incorrectly replaced. Replace only with same or equivalent type recommended by the manufacturer. Dispose of used batteries according to the manufacturer's instructions.

To fulfill the requirements of the EN60950, the QEVAL 2.0 incorporates two current-limiting devices (resistor and diode) in the battery power supply path.

# 4.4 Environmental Specifications

Temperature Operation: 0° to 60°C Storage: -20° to +80°C

Humidity Operation: 10% to 90% Storage: 5% to 95%

The above operating temperatures must be strictly adhered to at all times.

Humidity specifications are for non-condensing conditions.

QEV2m11

# 5 Connector Description

# **5.1** Connector CN1 Pinout

| Pin | Signal        | Description                           | Pin                                | Signal                 | Description                                              |

|-----|---------------|---------------------------------------|------------------------------------|------------------------|----------------------------------------------------------|

| 1   | GND           | Power Ground                          | 2                                  | GND                    | Power Ground                                             |

| 3   | GBE_MDI3-     | Gigabit Ethernet MDI3-                | 4 GBE MDI2- Gigabit Ethernet MDI2- |                        | Gigabit Ethernet MDI2-                                   |

| 5   | GBE_MDI3+     | Gigabit Ethernet MDI3+ 6 GBE MDI2+ Gi |                                    | Gigabit Ethernet MDI2+ |                                                          |

| 7   | GBE_LINK100#  | 100 Mbps link speed                   | 8                                  | GBE_LINK1000#          | 1000 Mbps link speed                                     |

| 9   | GBE_MDI1-     | Gigabit Ethernet MDI1-                | 10                                 | GBE_MDI0-              | Gigabit Ethernet MDI0-                                   |

| 11  | GBE_MDI1+     | Gigabit Ethernet MDI1+                | 12                                 | GBE_MDI0+              | Gigabit Ethernet MDI0+                                   |

| 13  | GBE_LINK#     | Gigabit Ethernet Link indicator       | 14                                 | GBE_ACT#               | Gigabit Ethernet Activity indicator                      |

| 15  | GBE_CTREF     | Reference voltage for GBE             | 16                                 | SUS_S5#                | S5 (Soft OFF) – shutdown state                           |

| 17  | WAKE#         | External system wake event            | 18                                 | SUS_S3#                | S3 (Suspend to RAM) – SLP                                |

| 19  | SUS_STAT#     | Suspend status                        | 20                                 | PWRBTN#                | Power button                                             |

| 21  | SLP_BTN#      | Sleep button                          | 22                                 | LID_BTN#               | LID button                                               |

| 23  | GND           | Power Ground                          | 24                                 | GND                    | Power Ground                                             |

| 25  | GND           | Power Ground                          | 26                                 | PWGIN                  | Power good input                                         |

| 27  | BATLOW#       | Battery low input                     | 28                                 | RSTBTN#                | Reset button input                                       |

| 29  | SATA0_TX+     | Serial ATA Channel 0 TX+              | 30                                 | SATA1_TX+              | Serial ATA Channel 1 TX+                                 |

| 31  | SATA0_TX-     | Serial ATA Channel 0 TX-              | 32                                 | SATA1_TX-              | Serial ATA Channel 1 TX-                                 |

| 33  | SATA ACT#     | Serial ATA Activity                   | 34                                 | GND                    | Power Ground                                             |

| 35  | SATA0_RX+     | Serial ATA Channel 0 RX+              | 36                                 | SATA1_RX+              | Serial ATA Channel 1 RX+                                 |

| 37  | SATA0_RX-     |                                       |                                    | SATA1_RX-              | Serial ATA Channel 1 RX-                                 |

| 39  | GND           | _                                     |                                    | GND                    | Power Ground                                             |

| 41  | BIOS_DISABLE# | ABLE# BIOS Module disable             |                                    | SDIO_CLK               | SDIO Clock Output                                        |

|     | /BOOT_ALT#    | Boot Alternative Enable               |                                    |                        |                                                          |

| 43  | SDIO_CD#      | SDIO Card Detect                      | 44                                 | SDIO_LED               | SDIO LED                                                 |

| 45  | SDIO_CMD      | SDIO Command/Response                 | 46                                 | SDIO_WP                | SDIO Write Protect                                       |

| 47  | SDIO_PWR#     | SDIO Power Enable                     | 48                                 | SDIO_DAT1              | SDIO Data Line 1                                         |

| 49  | SDIO_DAT0     | SDIO Data Line 0                      | 50                                 | SDIO_DAT3              | SDIO Data Line 3                                         |

| 51  | SDIO_DAT2     | SDIO Data Line 2                      | 52                                 | SDIO_DAT5              | SDIO Data Line 5                                         |

| 53  | SDIO_DAT4     | _                                     |                                    | SDIO Data Line 7       |                                                          |

| 55  | SDIO_DAT6     | SDIO Data Line 6                      | 56                                 | RSVD                   | Reserved                                                 |

| 57  | GND           | Power Ground                          | 58                                 | GND                    | Power Ground                                             |

| 59  | HDA_SYNC      | Serial Bus Synchronization.           | 60                                 | SMB_CLK                | SMBus Clock line.                                        |

|     | / AC97_SYNC   | Serial Bus Synchronization            |                                    | / GP1_I2C_CLK          | Multiplexed with General Purpose I <sup>2</sup> C bus #1 |

|     | / I2S_WS      | Multiplexed with I2S Word Select      |                                    |                        | clock line                                               |

| Pin | Signal       | Description                                       | Pin | Signal        | Description                                              |

|-----|--------------|---------------------------------------------------|-----|---------------|----------------------------------------------------------|

| 61  | HDA RST#     | HD Audio Codec Rest                               | 62  | SMB DAT       | SMBus Data line.                                         |

|     | /AC97 RST#   | AC'97 Codec Reset.                                |     | / GP1 I2C DAT | Multiplexed with General Purpose I <sup>2</sup> C bus #1 |

|     | / I2S_RST#   | Multiplexed with I2S Codec Reset                  |     |               | data line.                                               |

| 63  | HDA BCLK     | HD Audio Serial Bit Clock                         | 64  | SMB ALERT#    | SMBus Alert input                                        |

|     | / AC97_BCLK  | AC'97 Serial Bit Clock.                           |     | _             |                                                          |

|     | / I2S_CLK    | Multiplexed with I2S Serial Data Clock            |     |               |                                                          |

| 65  | HDA_SDI      | HD Audio Serial Data Input                        | 66  | GP0_I2C_CLK   | General Purpose I2C Bus No 0 clock line                  |

|     | / AC97_SDI   | AC'97 Serial Data Input.                          |     |               |                                                          |

|     | / I2S_SDI    | Multiplexed with I2S Serial Data Input            |     |               |                                                          |

| 67  | HDA_SDO      | HD Audio Serial Data Output                       | 68  | GP0_I2C_DAT   | General Purpose I2C Bus No 0 data line                   |

|     | / AC97_SDO   | AC'97 Serial Data Output.                         |     |               |                                                          |

|     | / I2S_SDO    | Multiplexed with I2S Serial Data Output.          |     |               |                                                          |

| 69  | THRM#        | Thermal Alarm active low                          | 70  | WDTRIG#       | Watchdog trigger signal                                  |

| 71  | THRMTRIP#    | Thermal Trip indicates an overheating condition   | 72  | WDOUT         | Watchdog event indicator                                 |

| 73  | GND          | Power Ground                                      | 74  | GND           | Power Ground                                             |

| 75  | USB_P7-      | USB Port 7 Differential Pair Multiplexed with     | 76  | USB_P6-       | USB Port 6 Differential Pair Multiplexed with            |

|     | / USB_SSTX0- | Superspeed USB transmit differential pair-        |     | / USB_SSRX0-  | Superspeed USB receive differential pair-                |

| 77  | USB_P7+      | USB Port 7 Differential Pair+. Multiplexed with   | 78  | USB_P6+       | USB Port 6 Differential Pair+. Multiplexed with          |

|     | / USB_SSTX0+ | Superspeed USB transmit differential pair+        |     | / USB_SSRX0+  | Superspeed USB receive differential pair+                |

| 79  | USB_6_7_OC#  | Over current detect input for USB port 6 and 7    | 80  | USB_4_5_OC#   | Over current detect input for USB port 4 and 5           |

| 81  | USB_P5-      | USB Port 5 Differential Pair Multiplexed with     | 82  | USB_P4-       | USB Port 4 Differential Pair Multiplexed with            |

|     | / USB_SSTX1- | Superspeed USB transmit differential pair-        |     | / USB_SSRX1-  | Superspeed USB receive differential pair-                |

| 83  | USB_P5+      | USB Port 5 Differential Pair+. Multiplexed with   | 84  | USB_P4+       | USB Port 4 Differential Pair+. Multiplexed with          |

|     | / USB_SSTX1+ | Superspeed USB transmit differential pair+        |     | / USB_SSRX1+  | Superspeed USB receive differential pair+                |

| 85  | USB_2_3_OC#  | Over current detect input for USB port 2 and 3 86 |     | USB_0_1_OC#   | Over current detect input for USB port 0 and 1           |

| 87  | USB_P3-      | USB Port 3 Differential Pair-                     | 88  | USB_P2-       | USB Port 2 Differential Pair-                            |

| 89  | USB_P3+      | USB Port 3 Differential Pair+                     | 90  | USB_P2+       | USB Port 2 Differential Pair+                            |

| 91  | USB_CC       | USB Client present detect pin                     | 92  | USB_ID        | USB ID pin                                               |

| 93  | USB_P1-      | USB Port 1 Differential Pair-                     | 94  | USB_P0-       | USB Port 0 Differential Pair-                            |

| 95  | USB_P1+      | USB Port 1 Differential Pair+                     | 96  | USB_P0+       | USB Port 0 Differential Pair+                            |

| 97  | GND          | Power Ground                                      | 98  | GND           | Power Ground                                             |

| 99  | eDP0_TX0+    | eDP Primary Channel 0+                            | 100 | eDP1_TX0+     | eDP Secondary channel 0+                                 |

|     | /LVDS_A0+    | LVDS Primary channel 0+                           |     | /LVDS_B0+     | LVDS Secondary channel 0+                                |

| 101 | eDP0_TX0-    | eDP Primary channel 0-                            | 102 | eDP1_TX0-     | eDP Secondary channel 0-                                 |

|     | / LVDS_A0-   | LVDS Primary channel 0-                           |     | / LVDS_B0-    | LVDS Secondary channel 0-                                |

| 103 | eDP0_TX1+    | eDP Primary channel 1+                            | 104 | eDP1_TX1+     | eDP Secondary channel 1+                                 |

|     | / LVDS_A1+   | LVDS Primary channel 1+                           |     | / LVDS_B1+    | LVDS Secondary channel 1+                                |

| 105 | eDP0_TX1-    | eDP Primary channel 1-                            | 106 | eDP1_TX1-     | eDP Secondary channel 1-                                 |

|     | / LVDS_A1-   | LVDS Primary channel 1-                           |     | / LVDS_B1-    | LVDS Secondary channel 1-                                |

| 107 | eDP0_TX2+    | eDP Primary channel 2+                            | 108 | eDP1_TX2+     | eDP Secondary channel 2+                                 |

|     | / LVDS_A2+   | LVDS Primary channel 2+                           |     | / LVDS_B2+    | LVDS Secondary channel 2+                                |

| Pin | Signal        | Description                                         | Pin  | Signal                   | Description                                   |

|-----|---------------|-----------------------------------------------------|------|--------------------------|-----------------------------------------------|

| 109 | eDP0 TX2-     | eDP Primary channel 2-                              | 110  | eDP1 TX2-                | eDP Secondary channel 2-                      |

|     | / LVDS_A2-    | LVDS Primary channel 2-                             |      | / LVDS_B2-               | LVDS Secondary channel 2-                     |

| 111 | LVDS_PPEN     | LVDS Power enable                                   | 112  | LVDS_BLEN                | LVDS Backlight enable                         |

| 113 | eDP0 TX3+     | eDP Primary channel 3+                              | 114  | eDP1 TX3+                | eDP Secondary channel 3+                      |

|     | / LVDS_A3+    | LVDS Primary channel 3+                             |      | / LVDS_B3+               | LVDS Secondary channel 3+                     |

| 115 | eDP0_TX3-     | eDP Primary channel 3-                              | 116  | eDP1_TX3-                | eDP Secondary channel 3-                      |

|     | /LVDS_A3-     | LVDS Primary channel 3-                             |      | / LVDS_B3-               | LVDS Secondary channel 3-                     |

| 117 | GND           | Power Ground                                        | 118  | GND                      | Power Ground                                  |

| 119 | eDP0_AUX+     | eDP Primary Auxilliary channel+                     | 120  | eDP1_AUX+                | eDP Secondary Auxiliary channel CLK+          |

|     | / LVDS_A_CLK+ | LVDS Primary channel CLK+                           |      | / LVDS_B_CLK+            | LVDS Secondary channel CLK+                   |

| 121 | eDP0_AUX-     | eDP Primary Auxilliary channel-                     | 122  | eDP1_AUX-                | eDP Secondary Auxiliary channel CLK-          |

|     | / LVDS_A_CLK- | LVDS Primary channel CLK-                           |      | / LVDS_B_CLK-            | LVDS Secondary channel CLK-                   |

| 123 | LVDS_BLT_CTRL | PWM Backlight brightness                            | 124  | GP_1-Wire_Bus            | General Purpose 1-wire bus interface          |

|     | / GP_PWM_OUT0 | General Purpose PWM Output                          |      |                          |                                               |

| 125 | LVDS_DID_DAT  | DDC Display ID Data line                            | 126  | eDP0_HPD#                | SSC clock chip data line. Can be used as eDP  |

|     | / GP2_I2C_DAT | General Purpose I2C Data line                       |      | / LVDS_BLC_DAT           | primary hotplug detect                        |

| 127 | LVDS_DID_CLK  | DDC Display ID Clock line                           | 128  | eDP1_HPD#                | SSC clock chip clock line. Can be used as eDP |

|     | / GP2_I2C_CLK | General Purpose I2C Clock line                      |      | / LVDS_BLC_CLK           | secondary hotplug detect                      |

| 129 | CAN0_TX       | CAN TX Output for CAN Bus Channel 0                 |      | CAN0_RX                  | CAN RX Input for CAN Bus Channel 0            |

| 131 | DP_LANE3+     | DisplayPort differential pair line lane 3+.         | 132  | RSVD (Differential)      | Reserved                                      |

|     | / TMDS_CLK+   | Multiplexed with TMDS differential pair clock+      |      |                          |                                               |

| 133 | DP_LANE3-     | DisplayPort differential pair line lane 3           | 134  | RSVD (Differential)      | Reserved                                      |

|     | / TMDS_CLK-   | Multiplexed with TMDS differential pair clock-      |      |                          |                                               |

| 135 | GND           | Power Ground                                        |      | GND                      | Power Ground                                  |

| 137 | DP_LANE1+     | DisplayPort differential pair line lane 1+          | 138  | DP_AUX+                  | DisplayPort auxiliary channel                 |

|     | / TMDS_LANE1+ | Multiplexed with TMDS differential pair lane1+      |      |                          |                                               |

| 139 | DP_LANE1-     | DisplayPort differential pair line lane 1-          | 140  | DP_AUX-                  | DisplayPort auxiliary channel                 |

|     | / TMDS_LANE1- | Multiplexed with TMDS differential pair lane1-      |      |                          |                                               |

| 141 | GND           | Power Ground                                        |      | GND                      | Power Ground                                  |

| 143 | DP_LANE2+     | DisplayPort differential pair line lane 2+          | 144  | RSVD (Differential Pair) | Reserved                                      |

|     | / TMDS_LANE0+ | Multiplexed with TMDS differential pair line lane0+ |      |                          |                                               |

| 145 | DP_LANE2-     | DisplayPort differential pair line lane 2-          | 146  | RSVD (Differential Pair) | Reserved                                      |

|     | / TMDS_LANE0- | Multiplexed with TMDS differential pair line lane0- |      |                          |                                               |

| 147 | GND           | Power Ground                                        |      | GND                      | Power Ground                                  |

| 149 | DP_LANE0+     | DisplayPort differential pair line lane 0+          | 150  | HDMI_CTRL_DAT            | DDC based control signal (data) for HDMI/DVI  |

|     | / TMDS_LANE2+ | Multiplexed with TMDS differential pair lane2+      | 1    |                          | device.                                       |

| 151 | DP_LANE0-     | DisplayPort differential pair line lane 0-          | 152  | HDMI_CTRL_CLK            | DDC based control signal (clock) for HDMI/DVI |

| 4=0 | / TMDS_LANE2- | Multiplexed with TMDS differential pair lane2-      | 4= 1 | DD UDD                   | device.                                       |

| 153 | DP_HDMI_HPD#  | Hot plug detection                                  |      | DP_HPD                   | DisplayPort Hot Plut Detect                   |

| 155 | PCIE_CLK_REF+ | PCI Express Reference Clock+                        |      | PCIE_WAKE#               | PCI Express Wake event                        |

| 157 | PCIE_CLK_REF- | PCI Express Reference Clock-                        |      | PCIE_RST#                | Reset Signal for external devices             |

| 159 | GND           | Power Ground                                        | 160  | GND                      | Power Ground                                  |

| Pin | Signal       | Description                                        | Pin | Signal               | Description                                            |

|-----|--------------|----------------------------------------------------|-----|----------------------|--------------------------------------------------------|

| 161 | PCIE3 TX+    | PCI Express Channel 3 Output+                      |     | PCIE3 RX+            | PCI Express Channel 3 Input+                           |

| 163 | PCIE3 TX-    | PCI Express Channel 3 Output-                      |     | PCIE3 RX-            | PCI Express Channel 3 Input-                           |

| 165 | GND          | Power Ground                                       |     | GND                  | Power Ground                                           |

| 167 | PCIE2_TX+    | PCI Express Channel 2 Output+                      | 168 | PCIE2_RX+            | PCI Express Channel 2 Input+                           |

| 169 | PCIE2 TX-    | PCI Express Channel 2 Output-                      |     | PCIE2 RX-            | PCI Express Channel 2 Input-                           |

| 171 | UARTO TX     | Serial Data Transmitter                            | 172 | UARTO RTS#           | Request To Send handshake signal                       |

| 173 | PCIE1_TX+    | PCI Express Channel 1 Output+                      | 174 | PCIE1_RX+            | PCI Express Channel 1 Input+                           |

| 175 | PCIE1_TX-    | PCI Express Channel 1 Output-                      | 176 | PCIE1_RX-            | PCI Express Channel 1 Input-                           |

| 177 | UART0_RX     | Serial Data Receiver                               | 178 | UART0_CTS#           | Clear To Send handshake signal                         |

| 179 | PCIE0_TX+    | PCI Express Channel 0 Output+                      | 180 | PCIE0_RX+            | PCI Express Channel 0 Input+                           |

| 181 | PCIE0_TX-    | PCI Express Channel 0 Output-                      | 182 | PCIE0_RX-            | PCI Express Channel 0 Input-                           |

| 183 | GND          | Power Ground                                       | 184 | GND                  | Power Ground                                           |

| 185 | LPC_AD0      | LPC Interface Address Data 0                       | 186 | LPC_AD1              | LPC Interface Address Data 1                           |

|     | / GPIO0      | General Purpose input/output 0                     |     | / GPIO1              | General Purpose input/output 1                         |

| 187 | LPC_AD2      | LPC Interface Address Data 2                       | 188 | LPC_AD3              | LPC Interface Address Data 3                           |

|     | / GPIO2      | General Purpose input/output 2                     |     | / GPIO3              | General Purpose input/output 3                         |

| 189 | LPC_CLK      | LPC Interface Clock                                | 190 | LPC_FRAME#           | LPC frame indicator                                    |

|     | /GPIO4       | General Purpose input/output 4                     | -   | /GPIO5               | General Purpose input/output 5                         |

| 191 | SERIRQ       | Serialized interrupt                               | 192 | LPC_LDRQ#            | LPC DMA request                                        |

| 400 | /GPIO6       | General Purpose input/output 6                     | 404 | /GPIO7               | General Purpose input/output 7                         |

| 193 | VCC_RTC      | 3V backup cell input                               | 194 | SPKR<br>/GP_PWM_OUT2 | Output for audio enunciator General Purpose PWM Output |

| 195 | FAN_TACHOIN  | Fan tachometer input                               | 196 | FAN_PWMOUT           | Fan speed control (PWM)                                |

|     | /GP_TIMER_IN | General Purpose Timer In                           |     | /GP_PWM_OUT1         | General Purpose PWM Output                             |

| 197 | GND          |                                                    |     | GND                  | Power Ground                                           |

| 199 | SPI_MOSI     | SPI Master serial output/Slave serial input        |     | SPI_CS0#             | SPI Chip Select 0 Output                               |

| 201 | SPI_MISO     | SPI Master serial input/Slave serial output signal |     | SPI_CS1#             | SPI Chip Select 1 Output                               |

| 203 | SPI_SCK      | SPI Clock Output                                   |     | MFG_NC4              | For manufacturing and debugging purposes               |

| 205 | VCC_5V_SB    | +5VDC,Standby ±5%                                  | 206 | VCC_5V_SB            | +5VDC Standby ±5%                                      |

| 207 | MFG_NC0      | For manufacturing and debugging purposes           |     | MFG_NC2              | For manufacturing and debugging purposes               |

| 209 | MFG_NC1      | For manufacturing and debugging purposes           |     | MFG_NC3              | For manufacturing and debugging purposes               |

| 211 | VCC          | Power supply +5VDC ±5%                             |     | VCC                  | Power supply +5VDC ±5%                                 |

| 213 | VCC          | Power supply +5VDC ±5%                             |     | VCC                  | Power supply +5VDC ±5%                                 |

| 215 | VCC          | Power supply +5VDC ±5%                             |     | VCC                  | Power supply +5VDC ±5%                                 |

| 217 | VCC          | Power supply +5VDC ±5%                             |     | VCC                  | Power supply +5VDC ±5%                                 |

| 219 | VCC          | Power supply +5VDC ±5%                             | 220 | VCC                  | Power supply +5VDC ±5%                                 |

| 221 | VCC          | Power supply +5VDC ±5%                             | 222 | VCC                  | Power supply +5VDC ±5%                                 |

| 223 | VCC          | Power supply +5VDC ±5%                             | 224 | VCC                  | Power supply +5VDC ±5%                                 |

| 225 | VCC          | Power supply +5VDC ±5%                             | 226 |                      | Power supply +5VDC ±5%                                 |

| 227 | VCC          | Power supply +5VDC ±5%                             | 228 |                      | Power supply +5VDC ±5%                                 |

| 229 | VCC          | Power supply +5VDC ±5%                             | 230 | VCC                  | Power supply +5VDC ±5%                                 |

### 5.2 Subsystems of QEVAL 2.0

### 5.2.1 **SMBus**

The QEVAL 2.0 supports both SMBus and I2C compliant devices. The SMBus signals are available in different locations on the QEVAL 2.0, including the feature connector (X19) described in section 6.13 of this document.

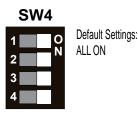

Use DIP switch SW4 on the QEVAL 2.0 to connect or disconnect SMBus devices that are not compatible with the I2C bus. For example, when you insert a Qseven® module that supports I2C bus on the QEVAL 2.0 instead of the SMBus (e.g conga-QMX6), then set SW4 DIP switches to OFF. This setting disconnects the SMBus devices.

### **DIP Switch SW4 Pin Description**

| DIP Switch | Status | Description                                                 |

|------------|--------|-------------------------------------------------------------|

| 1          | ON     | Connect module's SMB clock signal to PCle clock buffer      |

|            | OFF    | Disconnect module's SMB clock signal from PCIe clock buffer |

| 2          | ON     | Connect module's SMB data signal to PCle clock buffer       |

|            | OFF    | Disconnect module's SMB data signal from PCIe clock buffer  |

| 3          | ON     | Connect module's SMB clock signal to PCle Slots             |

|            | OFF    | Disconnect module's SMB clock signal from PCle Slots        |

| 4          | ON     | Connect module's SMB data signal to PCIe clock buffer       |

|            | OFF    | Disconnect module's SMB data signal from PCIe clock buffer  |

### 5.2.2 I<sup>2</sup>C Bus

The I<sup>2</sup>C signals are available in different locations on the QEVAL 2.0 including the feature connector (X19) described in section 6.13 of this document. Additionally, the QEVAL 2.0 includes a socket for an I<sup>2</sup>C EEPROM (U6) that can be used for test purposes during the system development.

The 8 pin DIP socket can be used with various 2-wire serial EEPROMS such as 24C04/08/16 and can be easily accessed by using the I<sup>2</sup>C control commands implemented in the Qseven<sup>®</sup> EASI API driver. Refer to the Qseven<sup>®</sup> module's user's guide and the EASI programmers guide for more information.

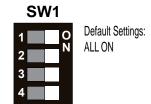

The address inputs (A0-A2) and write protect (WP) pin of I<sup>2</sup>C EEPROM can be configured with DIP switch SW1. By default, the DIP switches are set to ON (LOW state).

Copyright © 2014 congatec AG QEV2m11 21/49

| DIP Switch | Status | Description                  |

|------------|--------|------------------------------|

| 1          | ON     | Address input A0 set to LOW  |

|            | OFF    | Address input A0 set to HIGH |

| 2          | ON/    | Address input A1 set to LOW  |

|            | OFF    | Address input A1 set to HIGH |

| 3          | ON/    | Address input A2 set to LOW  |

|            | OFF    | Address input A2 set to HIGH |

| 4          | ON/    | Write protect set to LOW     |

|            | OFF    | Write protect set to HIGH    |

### 5.2.3 **SPI Bus**

The QEVAL 2.0 provides connection to the Serial Peripheral Interface (SPI) Bus via connector X8 and SO8 socket. The 8 pin SO8 socket (connector U4) can be used for SPI EEPROM. For example, you can a 3.3V serial flash in the SO8 socket to boot the system from external BIOS. The write protect (WP#) and hold (HOLD#) pins of the SO8 socket are internally pulled up to allow normal read/write operations.

Use DIP switch M13 to select whether to boot from the QEVAL 2.0 onboard SPI flash or from the on-module SPI flash. The yellow LED D4 glows when module boots from SPI flash onboard the QEVAL 2.0 (off-module SPI flash). The chip select (CS#) signal on the SPI EEPROM socket is connected to the Qseven® module's SPI\_CS0# signal and is active only if switch 1 of DIP switch M13 is turned on.

### SPI connector X8

| Pin | Signal   | Pin | Signal   |

|-----|----------|-----|----------|

| 1   | +3.3V    | 2   | +3.3V    |

| 3   | SPI_MOSI | 4   | SPI_CS0# |

| 5   | SPI_MISO | 6   | SPI_CS1# |

| 7   | SPI_SCK  | 8   | N.C.     |

| 9   | GND      | 10  | GND      |

#

### SO8 Socket U4

| Pin | Signal              | Pin | Signal             |

|-----|---------------------|-----|--------------------|

| 1   | Chip Select Input   | 5   | Data Input         |

| 2   | Data Output         | 6   | Serial Clock Input |

| 3   | Write Protect Input | 7   | Hold Input         |

| 4   | GND                 | 8   | VCC                |

U4 EEPROM SO8 Socket

### **DIP Switch M13**

| <b>DIP Switch</b> | Status | Description                                                          |  |

|-------------------|--------|----------------------------------------------------------------------|--|

| 1                 | ON     | Boot from SPI flash onboard the QEVAL 2.0 (off-module SPI flash)     |  |

|                   | OFF    | Boot from SPI flash onboard the Qseven® module (on-module SPI flash) |  |

| 2                 | ON     | SPI flash (U4) on hold                                               |  |

|                   | OFF    | SPI flash (U4) in normal operation                                   |  |

D4 LED

X8: 10 pin, 2 row 2.54mm grid female.

### 5.2.4 HDA Audio

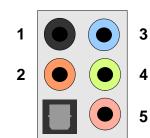

The QEVAL 2.0 has a HDA (High Definition Audio) codec (Realtek ALC888S) mounted on it. The 5.1 channel audio output interface of this codec is available on the connector described below. The drivers for this codec can be found in the 'Drivers' section under 'conga-QEVAL' on the congatec website at www.congatec.com.

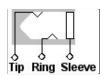

### **Audio X16**

| Stereo Jack 1 | Signal           | Stereo Jack 4 | Signal                 |

|---------------|------------------|---------------|------------------------|

| Tip           | Surround Left    | Tip           | Line Output Left       |

| Ring          | Surround Right   | Ring          | Line Output Right      |

| Sleeve        | Analog Ground    | Sleeve        | Analog Ground          |

| Stereo Jack 2 | Signal           | Stereo Jack 5 | Signal                 |

| Tip           | Center           | Tip           | Microphone Input Left  |

| Ring          | LFE              | Ring          | Microphone Input Right |

| Sleeve        | Analog Ground    | Sleeve        | Analog Ground          |

| Stereo Jack 3 | Signal           |               |                        |

| Tip           | Line Input Left  |               |                        |

| Ring          | Line Input Right |               |                        |

| Sleeve        | Analog Ground    |               |                        |

### Audio (X16)

(front view)

Connector Type

X16: 5 dedicated 3.5mm audio jacks (5.1 channel) and 1 optical S/PDIF output.

### **HDA Front Header Connector X24**

| Pin | Signal                   | Pin | Signal             |

|-----|--------------------------|-----|--------------------|

| 1   | Microphone 2 Input Left  | 2   | Analog Ground      |

| 3   | Microphone 2 Input Right | 4   | HDA_PRESENCE#      |

| 5   | Line 2 Output Right      | 6   | Microphone 2 Sense |

| 7   | Analog Ground            | 8   | N.C.               |

| 9   | Line 2 Output Left       | 10  | Line 2 Sense       |

# HDA Front Header (X24)

### Connector Type

X24 10 pin, 2 row 2.54mm grid female.

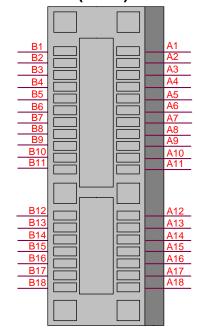

The QEVAL 2.0 also provides an audio interface on an edge card connector (CN10) for additional HDA, AC'97 or I2S codec support.

| Pin | Signal    | Pin | Signal    |

|-----|-----------|-----|-----------|

| B1  | +12V      | A1  | PRSNT1#   |

| B2  | +12V      | A2  | +12V      |

| В3  | +12V      | A3  | +12V      |

| B4  | GND       | A4  | GND       |

| B5  | I2C_CLK   | A5  | HDA_BCLK  |

| B6  | I2C_DAT   | A6  | HDA_SDOUT |

| B7  | GND       | A7  | HDA_SDIN  |

| В8  | +3.3V     | A8  | HDA_SYNC  |

| В9  | HDA_RST#  | A9  | +3.3V     |

| B10 | +3.3V AUX | A10 | +3.3V     |

| B11 | N.C.      | A11 | N.C.      |

|     | Key       |     |           |

| B12 | SPKR      | A12 | GND       |

| B13 | GND       | A13 | N.C.      |

| B14 | N.C.      | A14 | N.C.      |

| B15 | N.C.      | A15 | GND       |

| B16 | GND       | A16 | N.C.      |

| B17 | PRSNT2#   | A17 | N.C.      |

| B18 | GND       | A18 | GND       |

# HDA Edge Card Connector (CN10)

The I2C signals at pins B5 and B6 are necessary for I2S audio codec support. The QEVAL 2.0 supports also optional S/PDIF digital input (X23) and S/PDIF output 2 (X25) interfaces. The connectors for these interfaces are not assembled by default.

### 5.2.5 LPC Super I/O Device

The QEVAL 2.0 has an onboard Super I/O controller that provides additional interfaces such as two serial interfaces and KBC interface (mouse, keyboard). The Winbond W83627DHG Super I/O controller is connected to the LPC Bus of the Qseven® module.

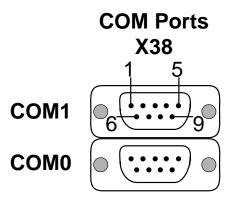

### **5.2.5.1 COM Ports**

The Super I/O controller provides two serial ports (COM0 and COM1) via connector X38. The serial ports are compliant to the RS232 standard and are only supported on modules that support LPC bus. For modules without LPC support, you can use the additional serial port (COM2), which is routed to header X30 for console functions. For more information about COM2 header, see section 6.8

| Pin | COM0 | COM1 |

|-----|------|------|

| 1   | DCD# | DCD# |

| 2   | RXD  | RXD  |

| 3   | TXD  | TXD  |

| 4   | DTR# | DTR# |

| 5   | GND  | GND  |

| 6   | DSR  | DSR  |

| 7   | RTS# | RTS# |

| 8   | CTS# | CTS# |

| 9   | RI#  | RI#  |

X38: 2x 9 pin D-SUB female.

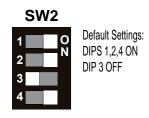

With DIP switch SW2, you can disable the Super I/O or configure its base address. The following table describes the settings for SW2.

### **DIP Switch SW2**

| <b>DIP Switch</b> | Status | Configuration                            |

|-------------------|--------|------------------------------------------|

| 1                 | ON/OFF | Super I/O Enabled/Disabled (ON=default)  |

| 2                 | ON/OFF | KBC Enabled/Disabled                     |

| 3                 | ON/OFF | Super I/O configured for address 4Eh/2Eh |

| 4                 | ON/OFF | Enable/disable POST display              |

Before you insert a module that does not support LPC (module with GPIO support such as conga-QMX6), you must set switch 1 and switch 4 of DIP switch SW2 to OFF. This setting turns off the onboard super I/O device.

### 5.2.5.2 KBC Interface

The super I/O controller provides keyboard interface via connector X39 and mouse interface via connector X40. The PS2 mouse and keyboard are connected to the KBC interface of the Super I/O controller.

### Keyboard (X39) Pin Description

| Pin | Signal           |

|-----|------------------|

| 1   | Keyboard Clock   |

| 2   | GND              |

| 3   | +5V power supply |

| 4   | Keyboard Data    |

### PS2 Keybooard (X39)

### Mouse (X40) Pin Description

| Pin | Signal           |

|-----|------------------|

| 1   | Mouse Clock      |

| 2   | GND              |

| 3   | +5V power supply |

| 4   | Mouse Data       |

X39, X40: 4 pin 1.25mm pitch PicoBlade connectors (Molex).

### 5.2.6 LPC/GPIO Header

To support LPC and GPIO devices, the LPC and GPIO signals are shared on the QEVAL 2.0. The shared signals are connected to pin header CN11. This header can be used for debugging or to connect devices such as Super I/O for evaluation.

### **LPC/GPIO Pin Description**

| Pin | LPC /GPIO          | Pin | LPC /GPIO         |

|-----|--------------------|-----|-------------------|

| 1   | LPC_AD0 / GPIO0    | 2   | +5V supply        |

| 3   | LPC_AD1 / GPIO1    | 4   | +3.3V supply      |

| 5   | LPC_AD2 / GPIO2    | 6   | GND               |

| 7   | LPC_AD3 / GPIO3    | 8   | GND               |

| 9   | LPC_CLK / GPIO4    | 10  | LPC_LDRQ# / GPIO7 |

| 11  | LPC_FRAME# / GPIO5 | 12  | LPC_RST#          |

| 13  | SERIRQ / GPIO6     | 14  | BOOT_ALT#         |

# LPC/GPIO Header CN11

Before you insert a module that does not support LPC (module with GPIO support such as conga-QMX6), you must set switch 1 and switch 4 of DIP switch SW2 to "off". This setting turns off the onboard super I/O device.

### Connector Type

CN11: 14 pin, 2 row 2.54mm grid female.

### 5.2.7 Universal Serial Bus (USB)

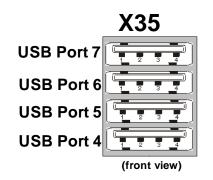

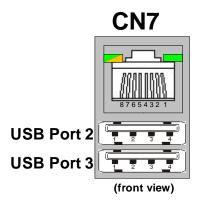

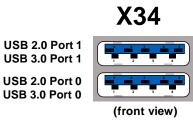

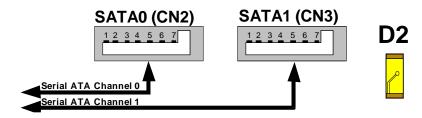

The QEVAL 2.0 provides 8 USB host ports (connectors CN7, X35 and X34) and one USB OTG port (connector X53). The USB host ports 0 and 1 (X34) support USB 3.0 and are shared with USB 4-7 (X35) according to Qseven® 2.0 specification (Check the datasheet of the attached module to determine if USB3.0 or USB 2.0 is supported). The Superspeed signals of USB host port 0 are shared with ports 6 and 7 (X35) while the Superspeed signals of USB host port 1 are shared with port 4 and 5 (X35).

### **USB Connectors**

Note

USB ports 2 and 3 support wake-on-USB. The support of USB port 3 wake-on-USB depends on the setting of DIP switch 9.3.

### **USB Pin Descriptions**

| USB | USB 3.0 Pin Description (X34) |     |               |  |

|-----|-------------------------------|-----|---------------|--|

| Pin | Signal                        | Pin | Signal        |  |

| 1   | +5V                           | 5   | USB3.0_SS_RX- |  |

| 2   | DATA-                         | 6   | USB3.0_SS_RX+ |  |

| 3   | DATA+                         | 7   | USB3.0 GND    |  |

| 4   | GND                           | 8   | USB3.0_SS_TX- |  |

|     |                               | 9   | USB3.0_SS_TX+ |  |

| USB 2.0 Pin Description ( X35, CN7) |        |  |

|-------------------------------------|--------|--|

| Pin                                 | Signal |  |

| 1                                   | +5V    |  |

| 2                                   | DATA-  |  |

| 3                                   | DATA+  |  |

| 4                                   | GND    |  |

| USB | OTG Pin Description (X53) |

|-----|---------------------------|

| Pin | Signal                    |

| 1   | VBUS                      |

| 2   | DATA-                     |

| 3   | DATA+                     |

| 4   | ID                        |

| 5   | GND                       |

The possible USB configurations are:

- Up to 8x USB 2.0 (connectors CN7, X35 and X34 (only USB 2.0))

- Up to 5x USB 2.0 and 1x USB 3.0 (connectors CN7, ports 4,5 of X35 and port 0 of X34)

- Up to 2x USB 2.0 and 2x USB 3.0 (connectors CN7 and X34)

- Up to 7x USB 2.0 and 1x USB OTG

- Up to 4x USB 2.0, 1x USB 3.0 and 1x USB OTG

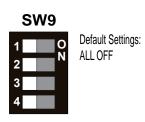

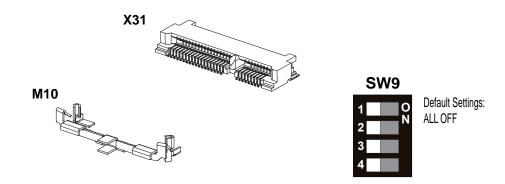

With DIP switch SW9, you can set the desired USB configuration as shown in the table below:

### **DIP Switch SW9**

| DIPs | Status | Description                                                                              |

|------|--------|------------------------------------------------------------------------------------------|

| 1    | ON     | Selects USB 3.0 port 0 (disables USB 2.0 port 6 and 7 of connector X35)                  |

|      | OFF    | Selects USB 2.0 port 6 and 7 (disables USB 3.0 port 0 of connector X34)                  |

| 2    | ON     | Selects USB 3.0 port 1 (disables USB 2.0 port 4 and 5 of connector X35)                  |

|      | OFF    | Selects USB 2.0 port 4 and 5 (disables USB 3.0 port 1 of connector X34 )                 |

| 3    | ON     | Routes USB 2.0 signals to port 2 of connector CN7 (disables mini-PCle)                   |

|      | OFF    | Routes USB 2.0 signals to mini-PCle connector X31 (disables USB 2.0 port 2)              |

| 4    | ON     | Routes USB 2.0 port 1 signals to connector X53 (micro USB AB connector)                  |

|      | OFF    | Routes USB 2.0 port 1 signals to standard USB A connector X34 (disables USB OTG support) |

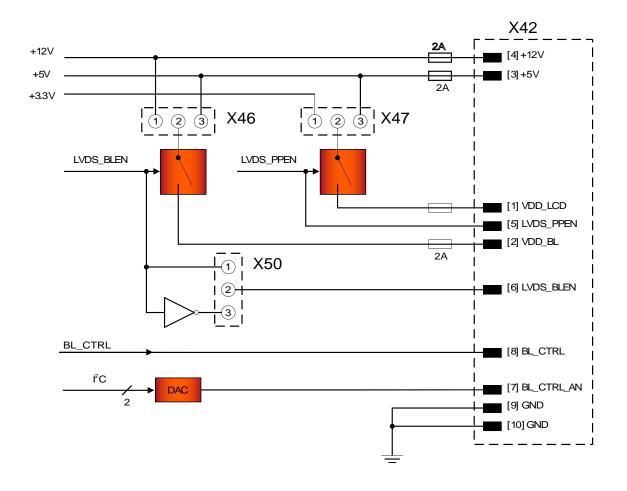

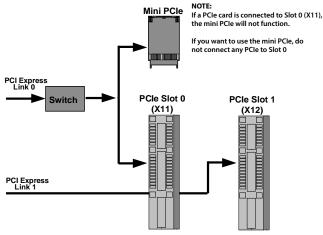

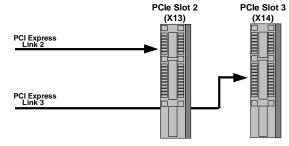

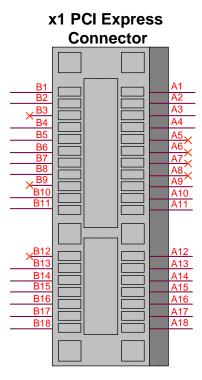

### **USB OTG Jumper Settings**