# PCL-728 2-CHANNEL D/A CARD USER'S MANUAL

#### COPYRIGHT NOTICE

This document is copyrighted 1992 by Advantech Co.,Ltd. All rights are reserved. Advantech Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice.

No part of this manual may be reproduced, copied, translated or transmitted, in any form or by any means without the prior written permission of Advantech Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Advantech Co., Ltd. assumes no responsibility for its use, nor for any infringements of rights of third parties which may result from its use.

PC-LabCard is a trademark of Advantech Co., Ltd. IBM PC, PC/XT and PC/AT are trademarks of International Business Machines Corporation.

Part No. 2003728000 Rev. A1 Printed in Taiwan May, 1992

# TABLE OF CONTENTS

| CHAPTER 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1. Initial Inspection                                                                                                                                                                                                                                                                                                                             |

| 1.2. Specifications                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                     |

| CHAPTER 2. SWITCHES, JUMPERS, AND CONNECTORS                                                                                                                                                                                                                                                                                                        |

| 2.1. I/O Address Selection                                                                                                                                                                                                                                                                                                                          |

| 2.2. Jumper Settings                                                                                                                                                                                                                                                                                                                                |

| 2.2.1. Reference Source Selection                                                                                                                                                                                                                                                                                                                   |

| 2.2.2. Voltage Output Selection                                                                                                                                                                                                                                                                                                                     |

| 2.2.3. Current Sink Range Selection                                                                                                                                                                                                                                                                                                                 |

| 2.3. Connectors CN1 and CN2                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                     |

| CHAPTER 3. REGISTER STRUCTURE AND FORMAT 1                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                     |

| 3.1. I/O Address Map                                                                                                                                                                                                                                                                                                                                |

| <b>^</b>                                                                                                                                                                                                                                                                                                                                            |

| 3.2. Data Format                                                                                                                                                                                                                                                                                                                                    |

| 3.2. Data Format                                                                                                                                                                                                                                                                                                                                    |

| 3.2. Data Format                                                                                                                                                                                                                                                                                                                                    |

| 3.2. Data Format       1         3.2.1. BASE+0 High Byte Data       1         3.2.2. BASE+1 Low Byte Data       1         3.2.3. BASE+2 High Byte Data       1                                                                                                                                                                                      |

| 3.2. Data Format       1         3.2.1. BASE+0 High Byte Data       1         3.2.2. BASE+1 Low Byte Data       1         3.2.3. BASE+2 High Byte Data       1         3.2.4. BASE+3 Low Byte Data       1                                                                                                                                          |

| 3.2. Data Format       1         3.2.1. BASE+0 High Byte Data       1         3.2.2. BASE+1 Low Byte Data       1         3.2.3. BASE+2 High Byte Data       1         3.2.4. BASE+3 Low Byte Data       1         3.3. Unipolar and Bipolar Binary Code Tables       1                                                                             |

| 3.2. Data Format       1         3.2.1. BASE+0 High Byte Data       1         3.2.2. BASE+1 Low Byte Data       1         3.2.3. BASE+2 High Byte Data       1         3.2.4. BASE+3 Low Byte Data       1                                                                                                                                          |

| 3.2. Data Format       1         3.2.1. BASE+0 High Byte Data       1         3.2.2. BASE+1 Low Byte Data       1         3.2.3. BASE+2 High Byte Data       1         3.2.4. BASE+3 Low Byte Data       1         3.3. Unipolar and Bipolar Binary Code Tables       1         3.4. Programming Examples       1                                   |

| 3.2. Data Format       1         3.2.1. BASE+0 High Byte Data       1         3.2.2. BASE+1 Low Byte Data       1         3.2.3. BASE+2 High Byte Data       1         3.2.4. BASE+3 Low Byte Data       1         3.3. Unipolar and Bipolar Binary Code Tables       1         3.4. Programming Examples       1     CHAPTER 4. SIGNAL CONNECTIONS |

| 3.2. Data Format       1         3.2.1. BASE+0 High Byte Data       1         3.2.2. BASE+1 Low Byte Data       1         3.2.3. BASE+2 High Byte Data       1         3.2.4. BASE+3 Low Byte Data       1         3.3. Unipolar and Bipolar Binary Code Tables       1         3.4. Programming Examples       1                                   |

#### CHAPTER 1. INTRODUCTION

The PCL-728 is an isolated 12 bit dual-channel analog output (D/A) card designed for applications run in harsh environments. Each channel is fully isolated, and independent from the system's ground, and can be set to the following output ranges: 0 to 5V, 0 to 10V,  $\pm$ 5V,  $\pm$ 10V, 4 to 20mA, and 0 to 20mA (current sink). After you turn on or reset your PC, each channel will also resets to 0V in unipolar or bipolar modes.

The PCL-728 comes equipped with two D-9 pin female connector for output signal wiring applications.

## 1.1. Initial Inspection

Before proceeding any further, please examine the contents of this package to ensure that the following items have been shipped:

- 1 PCL-728 2-Channel D/A Card

- 1 User's Manual

- 1 utility diskette

The PCL-728 has been thoroughly inspected and tested before it was shipped, and should be in perfect electronic order. If the card is damaged or appears to be defective, contact your local PC-LabCard dealer immediately.

# 1.2. Specifications

Device:

AD7541KN or equivalent.

Channels:

2.

Resolution:

12 bits.

Linearity:

$\pm \frac{1}{2}$  LSB.

Accuracy:

$\pm 0.012\%$  full scale range.

Temperature drift:

5 PPM/°C (0 to 50°C).

**Isolation voltage:**

≥500 Vdc.

Output range:

0 to +5V (unipolar).

-5V to +5V (bipolar). 0 to +10V (unipolar). -10V to +10V (bipolar).

0 to 20mA current loop (sink). 4 to 20mA current loop (sink).

Reference voltage:

Internal: -5V, and -10V.

External: DC or AC,  $\pm 10V$  (max.).

Output drive current:  $\pm 5$ mA (max.).

Current loop excitation voltage: +8V (min.), 36V (max.) for 4 to 20mA

and 0 to 20mA current loop.

**Settling time:**

≤60µs.

Power consumption:

+5V @ 800mA (max.).

Storage temperature:

Operating temperature:0 to 50°C (-32 to 122°F). -20 to 65°C (-68 to 149°F).

**Dimensions:**

184mm x 119mm.

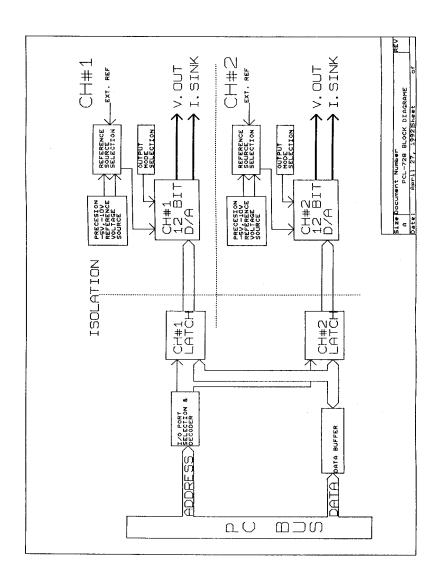

PCL-728 Block Diagram

# CHAPTER 2. SWITCHES, JUMPERS, AND CONNECTORS

The PCL-728 uses ten sets of jumper pins (five sets for each channel) to configure its reference source, voltage output, and current sink range selections to your applications requirements. It also uses an 8-position DIP switch for selecting an appropriate I/O address for its firmware to occupy. The following sections offer the necessary information for setting the PCL-728's jumpers and DIP switch positions.

#### 2.1. I/O Address Selection

Selecting an appropriate I/O address for your PCL-728 to occupy is important because it avoids any conflicts that could occur if another add-on card occupies the same I/O space. DIP switch, SW1, should be set to a valid I/O address between 200 to 3F8 (hexadecimal). The following table outlines the various addresses you may choose from according to each position on SW1.

| I/O Address         |            |           | Swi       | tch F     | osit     | ion       | <b></b> - |        |

|---------------------|------------|-----------|-----------|-----------|----------|-----------|-----------|--------|

| Range (Hex)         | 1<br>A9    | 2<br>A8   | 3<br>A7   | 4<br>A6   | 5<br>A5  | 6<br>A4   | 7<br>A3   | 8<br>X |

| 200-207<br>210-21F  | OFF<br>OFF | ON        | ON        | ON<br>ON  | ON<br>ON | ON<br>OFF | ON<br>ON  | x<br>x |

| 2CO-2CF*<br>300-30F | OFF<br>OFF | ON<br>OFF | OFF<br>ON | OFF<br>ON | ON<br>ON | ON<br>ON  | ON<br>ON  | X<br>X |

## Key:

X = Non specific

A9 through A3 correspond to your PC's address lines

\* Factory default

# 2.2. Jumper Settings

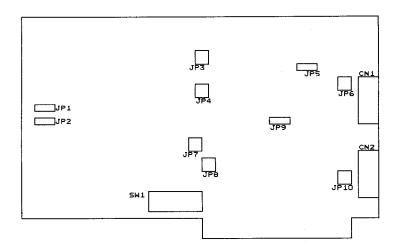

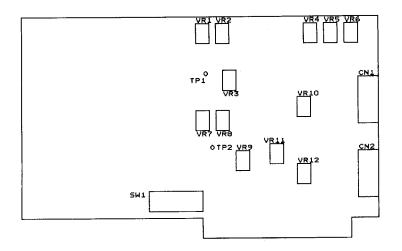

Jumpers, JP1 through JP10 (see illustration below), are used to set the reference source, voltage output, and current sink range selections on board the PCL-728. The following sections will provide you with the necessary information for setting these jumpers.

Jumper Locations

#### 2.2.1. Reference Source Selection

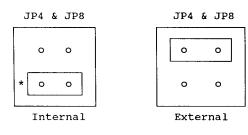

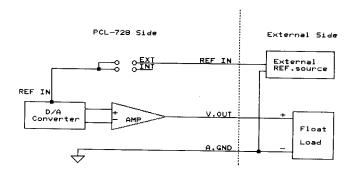

Before setting the PCL-728's reference source, you must decide which type of source, internal or external (JP4 for Channel 1, and JP8 for Channel 2), you want to use with your application. External reference voltages may be selected for AC or DC sources. the maximum external reference voltage is  $\pm 10V$ , and the maximum D/A output range is  $\pm 10V$ . See the illustration below:

\* Factory default

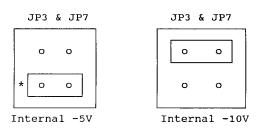

A fixed, precision internal -5 and -10V reference is provided by the PCL-728. Setting Channels 1 and 2's internal reference source is accomplished by closing JP3 (for Channel 1), and JP7 (for Channel 2). The internal reference source can be set to -10V or -5V. The following illustration pertains to both of these jumpers.

\* Factory default

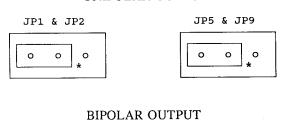

## 2.2.2. Voltage Output Selection

Jumpers, JP1 and JP5 (for Channel 1), and JP2 and JP9 (for Channel 2), are all used to select each channel's voltage output as either unipolar or bipolar. The following illustration shows the voltage output selection for both channels.

#### UNIPOLAR OUTPUT

\* Factory default

Some typical reference source and output range configurations are illustrated below:

| Output Range          | JP3 (JP7) | JP1 & JP5 (JP2 & JP9) |

|-----------------------|-----------|-----------------------|

| 0 to +5V<br>Unipolar  | 0 0       | 0 0 0                 |

| 0 to +10V<br>Unipolar | 0 0       | 0 0 0                 |

| ±5V<br>Bipolar        | 0 0       | 0 0 0                 |

| ±10V<br>Bipolar       | 0 0       | 0 0 0                 |

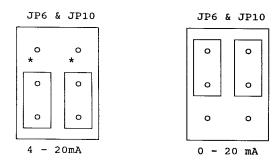

#### 2.2.3. Current Sink Range Selection

JP6 and JP10 are used to select each channel's current sink range of either 4-20mA or 0-20mA. JP6 corresponds with Channel 1, and JP10 is used with Channel 2. In order to use the current sink range, you must set the PCL-728's output voltage to unipolar. You must also use the internal reference source set to -5V. The diagram below shows the correct jumper settings for the PCL-728's current sink range.

\* Factory default

NOTE:

In order to maintain an accurate output during your application, it is important that you keep the PCL-728's variable resistors (VRs) be calibrated from time to time. Calibration instructions are provided in Appendix A.

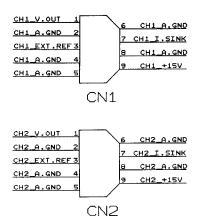

#### 2.3. Connectors CN1 and CN2

The PCL-728 uses two D-9 female connectors, located on the card at CN1 and CN2. Use these connectors for outputing a D/A signal to an external device. CN1 is used as an output connection for Channel 1, and CN2 is used for Channel 2. The following diagram shows an illustration for both of these connectors. (Both connectors have the same pin assignments.)

#### Key:

V.OUT = Analog voltage output

EXT. REF = External reference source voltage input

I.SINK = Current sink A.GND = Analog ground +15V = +15V output

Connectors CN1 and CN2

# CHAPTER 3. REGISTER STRUCTURE AND FORMAT

The following sections provide information about the PCL-728's register structure and format. This consists of the card's I/O address map, and its data format. You may use this information to write your own software driver. Programming examples are provided for your convenience at the end of this chapter.

#### 3.1. I/O Address Map

The PCL-728 uses four consecutive output (write-only) addresses - Base+0, Base+1, Base+2, and Base+3 - for your programming and application requirements. The table below outlines each of these addresses according to how they are used.

| Address | USAGE              |

|---------|--------------------|

| BASE+0  | CH1 HIGH BYTE DATA |

| BASE+1  | CH1 LOW BYTE DATA  |

| BASE+2  | CH2 HIGH BYTE DATA |

| BASE+3  | CH2 LOW BYTE DATA  |

#### 3.2. Data Format

The following sections contain tables which illustrate the data format for each of the PCL-728's four base addresses. Unipolar and Bipolar Binary Code Tables are provided in Section 3.3 to assist you when writing instructions to the PCL-728's data registers.

Please note that, when programming the PCL-728, the high byte data is sent first. Once this has been done, the it will be temporarily held in the card's register, and is not released to the D/A converter. After you have written the low byte data, the high data will be combined to the low byte data, and then passed on to the D/A converter. This double buffering process protects the PCL-728's D/A data integrity by using a single step update.

### 3.2.1. BASE+0 High Byte Data

The following table pertains to Channel 1's high byte data bits from base address Base +0.

| D7 | D6 | D5 | D4 | D3   | D2   | D1  | D0  |

|----|----|----|----|------|------|-----|-----|

| X  | X  | X  | X  | DA11 | DA10 | DA9 | DA8 |

#### Key:

X = Non-specific

DA11 to DA8 = Digital to analog data. DA11 is the Most Significant Bit (MSB).

## 3.2.2. BASE+1 Low Byte Data

The following table pertains to Channel 1's low byte data bits from base address Base + 1.

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DA7 | DA6 | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 |

# Key:

X = Non-specific

DA7 to DA0 = Digital to analog data. DA0 is the Least Significant Bit (LSB).

# 3.2.3. BASE+2 High Byte Data

The following table pertains to Channel 2's high byte data bits from base address Base +2.

| D7 | D6 | D5 | D4 | D3   | D2   | D1  | D0  |

|----|----|----|----|------|------|-----|-----|

| X  | X  | X  | X  | DA11 | DA10 | DA9 | DA8 |

#### Key:

X = Non-specific

DA11 to DA8 = Digital to analog data. DA11 is the Most Significant Bit (MSB).

# 3.2.4. BASE+3 Low Byte Data

The following table pertains to Channel 2's low byte data bits from base address Base +2.

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DA7 | DA6 | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 |

# Key:

X = Non-specific

DA7 to DA0 = Digital to analog data. DA0 is the Least Significant Bit (LSB).

# 3.3. Unipolar and Bipolar Binary Code Tables

## Unipolar Binary Code Table

| Digital | Input C | Code |                                         |

|---------|---------|------|-----------------------------------------|

| MSB     |         | LSB  | Nominal Analog Output                   |

| 1111    | 1111    | 1111 | -V <sub>REF</sub> * (4095/4096)         |

| 1000    | 0000    | 0001 | -V <sub>REF</sub> * (2049/4096)         |

| 1000    | 0000    | 0000 | $-V_{REF}$ * (2048/4096) = $-V_{REF}/2$ |

| 0111    | 1111    | 1111 | -V <sub>REF</sub> * (2047/4096)         |

| 0000    | 0000    | 0001 | -V <sub>REF</sub> * (1/4096)            |

| 0000    | 0000    | 0000 | $-V_{REF}$ * (0/4096) = 0               |

#### NOTES:

- 1.

- 2

- $V_{REF}$  is the reference source voltage that you selected. Nominal full scale is given by FS =  $-V_{REF}$  \* (4095/4096). Nominal LSB magnitude is given by LSB =  $-V_{REF}$  \* (1/4096). 3.

Bipolar Binary Code Table

| Digital<br>MSB | Input C | ode<br>LSB | Nominal Analog Output            |

|----------------|---------|------------|----------------------------------|

| 1111           | 1111    | 1111       | -V <sub>REF</sub> * (2047/2048)  |

| 1000           | 0000    | 0001       | -V <sub>REF</sub> * (1/2048)     |

| 1000           | 0000    | 0000       | 0                                |

| 0111           | 1111    | 1111       | + V <sub>REF</sub> * (1/2048)    |

| 0000           | 0000    | 0001       | + V <sub>REF</sub> * (2047/2048) |

| 0000           | 0000    | 0000       | + V <sub>REF</sub> * (2048/2048) |

|                |         |            |                                  |

#### NOTES:

- 1. V<sub>REF</sub> is the reference source voltage that you selected.

- Nominal full scale is given by FS =  $-V_{REF}$  \* (2047/2048).

- 3. Nominal LSB magnitude is given by LSB =  $-V_{REF} * (1/2048)$ .

# 3.4. Programming Examples

The PCL-728's utility diskette has two files containing demonstration programs. The files are named DEMO728.C, and TESTPROG.EXE. Use these file to run programs which demonstrate various PCL-728 functions and commands.

#### CHAPTER 4. SIGNAL CONNECTIONS

Making a correct signal correction is important to send data accurately. Since most data acquisition applications involve some form of voltage measurement, making a sound signal connection will also protect your equipment against possible damages. This chapter provides helpful information showing how to make proper signal connection when using your PCL-728.

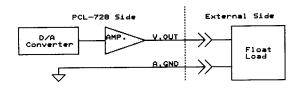

## 4.1. Voltage Output Connection

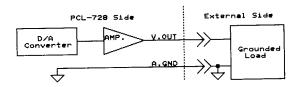

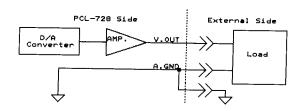

The PCL-728 supports two channels of D/A voltage output, of which there is only one output signal wire used with each channel. Voltage is referenced to a common ground. A voltage output connection is a very simple connection which is made to a floating load (see the illustration given below).

If your application requires that use a grounded load, then your signal connection should be made as shown in the illustration below:

Some differential input loads require that you use an external ground wire when making your signal connection (see illustration below).

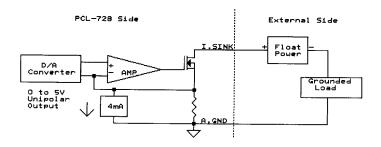

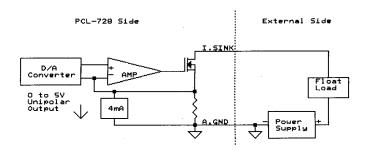

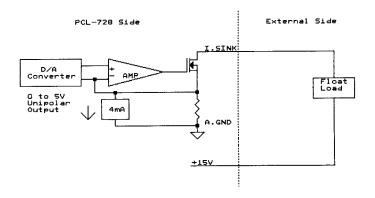

#### 4.2. 4 to 20mA and 0 to 20mA Current Sink Connections

The PCL-728's current loop output uses a 0 to 5V (unipolar) voltage output as each channel's driving source. Current drive circuits consist of a power field-effect transistor (FET). The current output's voltage bias must be held within a range of 8 to 36V for accurate results. The card also provides an internal 15V power source for current loop sources which can be implemented via Pin 9, located on connectors CN1 and CN2.

You can use three types of current sink connections: a grounded load with a floating power supply, a floating load with a grounded power supply, and a floating load with an internal 15V power supply. Each of these connection are shown in the following illustrations.

Grounded Load with a Floating Power Supply

Floating Load with a Grounded Power Supply

Floating Load with a 15V Power Supply

## 4.3. Programmable Attenuator Connection

The PCL-728 can perform digital attenuator applications by inputing variable AC or DC references. If you want to use this function set jumpers, JP4 for Channel 1, and JP8 for Channel 2, to the external reference setting (see Section 2.2.1.).

The PCL-728 can also be used to generate arbitrary waveform outputs. An illustration of an attenuator connection used in these applications is shown below.

External reference input signals can either be AC (< 100 KHz) or DC . This allows the PCL-728's D/A converter to be used as a programmable attenuator. The attenuation factor between the reference input and analog output is:

#### ATTENUATION FACTOR = G/4096

where G is the data written to the PCL-728's D/A registers, and the value is between 0 and 4095. For example, if G represents 2048, then the attenuation factor will be 0.5. A sine wave amplitude of 10V applied to the external reference input will generate a sine wave amplitude of 5V from the card's output pin.

#### APPENDIX A. CALIBRATION

The PCL-728 uses twelve variable resistors (VR), six for each channel, which allow you to calibrate each of its two output channels. The following information outlines each VR as it relates to its function. Refer to the illustration shown below for the locations of the PCL-728's VRs.

A PC-bus extension card will make calibrating the PCL-728's VRs easier. The PCL-757 PC-bus Extension/Switch Card is offered by PC-LabCard for this purpose.

**VR** Locations

|                                                     | PCL-728                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH1's internal -10 reference source adjustment.     |                                                                                                                                                                                                                                                                                 |

|                                                     |                                                                                                                                                                                                                                                                                 |

| CH1's gain adjustment.                              |                                                                                                                                                                                                                                                                                 |

| CH1's unipolar offset adjustment.                   |                                                                                                                                                                                                                                                                                 |

| CH1's bipolar offset adjustment.                    |                                                                                                                                                                                                                                                                                 |

| CH1's current sink offset adjustment (4mA to 20mA). |                                                                                                                                                                                                                                                                                 |

| CH2's internal -5V reference source adjustment.     |                                                                                                                                                                                                                                                                                 |

|                                                     |                                                                                                                                                                                                                                                                                 |

| CH2's gain adjustment.                              |                                                                                                                                                                                                                                                                                 |

| CH2's bipolar offset adjustment.                    |                                                                                                                                                                                                                                                                                 |

| CH2's unipolar offset adjustment.                   |                                                                                                                                                                                                                                                                                 |

|                                                     | CH1's unipolar offset adjustment. CH1's bipolar offset adjustment. CH1's current sink offset adjustment (4mA to 20mA). CH2's internal -5V reference source adjustment. CH2's internal -10V reference source adjustment. CH2's gain adjustment. CH2's bipolar offset adjustment. |

In order to calibrate the PCL-728, you should use a precision voltmeter to obtain accurate readings. Standard procedures for performing a calibration are given below.

CH2's current sink offset adjustment (4mA to 20mA).

# **Internal Reference Source Calibration**

Calibration

VR12

When calibrating the PCL-728's internal reference source, you ground one of your voltmeter's probes, while the other probe is connected to TP1 (Test Point 1 for Channel 1), or TP2 (Test Point 2 for Channel 2).

- A. Use VR2 and/or VR7 to adjust each channel's -5V reference source to obtain a voltage of -5V.

- B. VR1 and/or VR8 are used to calibrate each channel's -10V reference source to obtain a voltage of -10V.

# **Unipolar Output Offset Calibration**

- Select an appropriate reference voltage source for each channel to be calibrated.

- B. Set all digital input codes to 0. Then adjust VR4 and/or VR11 (depending on what channels are to be calibrated) until your voltmeter reads 0 volts.

# Unipolar Output Gain Calibration

- A. Select an appropriate reference voltage source for the channels to be

- B. Set all digital input codes to 1 (see Unipolar Binary Code Table in Section 3.3). Now, adjust VR3 and/or VR9 until your voltmeter shows a reading equal to the output voltage shown in the Unipolar Binary Code Table in Section 3.3.

# 4mA Constant Current Calibration

- A. Set the digital output code to 00000000000, and set each channel's reference voltage to -5V, and unipolar output.

- B. Adjust VR6 and/or VR12 to maintain a constant current of 4mA.

# **Bipolar Output Offset Calibration**

- A. Select a reference voltage source for the channels you will calibrate.

- B. Set the digital input code to 10000000000. Adjust VR5 and/or VR10 until your voltmeter reads 0 volts.

# Bipolar Output Gain Calibration

- A. Select a reference voltage source for the channels you will calibrate.

- B. Set the digital input code to 0. Then adjust VR3 and/or VR9 until your voltmeter shows a reading equal to the output voltage shown in the Bipolar Binary Code Table in Section 3.3.

- C. Now, set all digital input codes to 1. Adjust VR3 and/or VR9 until your voltmeter shows a reading equal to the output voltage shown in the Bipolar Binary Code Table in Section 3.3.